CLOSE

About Elements

私たち田中貴金属は、貴金属のリーディングカンパニー。

社会の発展を支える先端素材やソリューション、

それらが生まれた開発ストーリー、技術者たちの声、そして経営理念とビジョンーー

Elementsは、「貴金属を究める」をスローガンに、

より良い社会、豊かな地球の未来につながるインサイトを発信するWEBメディアです。

エレクトロニクス産業に革命をもたらす画期的なスピントロニクス製造プロセスを開発

米ミネソタ大学ツインシティー校の研究チームは、米国立標準技術研究所(NIST)のチームと共同で、スピントロニクスデバイスを製造するための革新的な製法を開発した。この製法は、コンピューターやスマートフォンなど多くの電子機器を構成する半導体チップの新たな業界標準となる可能性を秘めている。この新しい製法により、スピントロニクスデバイスの高速化と高効率化が可能になり、デバイスを従来よりもさらに小型化できるようになるはずだ。

研究チームの論文は、査読審査のあるトップレベルの材料科学専門誌『Advanced Functional Materials』に掲載された。

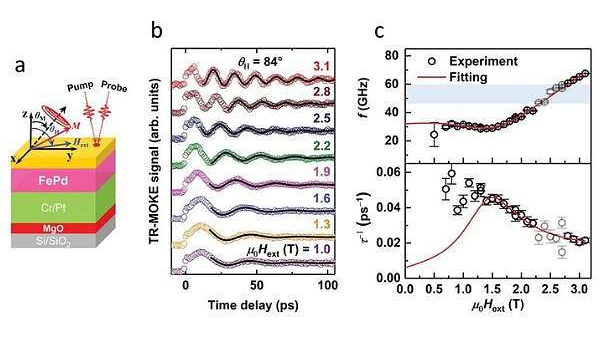

時間分解磁気光学カー効果(TR-MOKE)測定の模式図

論文の主執筆者であり、ミネソタ大学電気・コンピューター工学部教授でロバート・F・ハートマン講座のチェアを務めるジェンピン・ワン(Jian-Ping Wang)は、「この研究で発見した材料とデバイスによって半導体業界は、メモリや演算の応用に向けた、これまでになかったスピントロニクスのチャンスを拡大できると我々は確信しています」と話す。「スピントロニクスは、新しい機能を備えるマイクロエレクトロニクス(超小型電子機器)を製造する上で極めて重要です」

ワン教授によると、ミネソタ大は米国の半導体研究コンソーシアム(SRC)」、米国防高等研究計画局(DARPA)、米国立科学財団(NSF)の強力な支援を受けつつ、この研究を10年以上にわたって大規模に主導してきたという。

またワン教授のチームは、ミネソタ大の技術商業化組織「テクノロジー・コマーシャリゼーション」およびNISTと連携し、今回の技術の特許と、この研究に関連する他の複数の特許を取得した。今回の発見は、今後10年間にわたるスピントロニクスデバイスの設計・製造研究の新たな道筋を開くものだ。

「これが意味するのは、ハネウェル(Honeywell)、スカイウォーター(Skywater)、グローバル・ファウンドリーズ(Globalfoundries)、インテル(Intel)などの半導体メーカーが、この材料を自社の半導体製造プロセスや製品に組み入れる可能性があるということです」と、ワン教授は言う。「これは非常にエキサイティングなことです。業界の技術者たちが、これまでよりはるかに強力なシステムを設計できるようになるからです」

半導体業界では、電子機器のエネルギー効率、演算速度、データ記憶容量を最大限に高めることが可能な、より一層小型のチップの開発が常に試みられている。スピントロニクスデバイスとは、データを記憶する際に、電子の電荷ではなく、スピンを利用するものだ。従来型のトランジスタベースのチップに代わる、より高効率で有望な代替手段を提供することが期待されている。この材料はまた、不揮発性である可能性がある。つまり、電源を切った後も記憶の保持や演算の実行が可能であり、消費電力が少ないということだ。

スピントロニクス材料が半導体チップに初めて組み込まれて以来、これまでに10年余りが経過しているが、業界標準のスピントロニクス材料であるコバルト鉄ホウ素(CoFeB)は、すでに縮小可能性の限界に達している。現在のところ、データ保持能力を損なわずにデバイスの大きさを20ナノメートル(1nm=1mmの100万分の1)より小さくすることは、技術的に不可能だ。

ミネソタ大の研究チームは、コバルト鉄ホウ素の代わりに鉄パラジウム(FePd)を材料に用いると、サイズを5ナノメートルまで縮小できることを示し、この問題を巧みに回避した。鉄パラジウムは、消費電力がより小さく、データ記憶容量がより大きい可能性がある。

さらに研究チームは、8インチ(200ミリメートル)サイズの基板に対応したマルチチャンバー型超高真空スパッタリング装置を用いて、シリコン基板上に鉄パラジウムを成長させることに初めて成功した。この装置はミネソタ大しか備えていないもので、全米の学術機関の中では他に類を見ないものだ。

論文の筆頭執筆者で、ミネソタ大電気・コンピューター工学科の博士課程学生のデュアン・リュー(Deyuan Lyu)は、次のように説明する。「この研究は、5ナノメートル弱まで縮小可能なこの材料を半導体業界互換の基板上で成長させ得ることを、世界で初めて示しました。いわゆる『CMOS+X戦略』と呼ばれるものです」

NISTのスタッフ・サイエンティストで、今回の研究の主要な貢献者の一人、ダニエル・ゴップマン(Daniel Gopman)は、「我々のチームは、次世代のデータ大量消費型アプリに必要とされるスピントロニクスデバイスを製造する新材料の性能を高めることに挑戦しました」と話す。「今回の進展によって、半導体チップの技術的状況におけるスピントロニクスデバイスのさらなる成長をどのように後押しできるのか、非常に楽しみです」

この研究は、DARPAから4年間で400万ドル(約5億5130万円)の助成金を受けたほか、NIST、SRCの研究プログラム「nCORE」の7カ所の研究拠点の一つ「SMART」、NSFからも資金供与を受けた。

研究チームは、ワン教授、ゴップマン、リューに加えて、ミネソタ大理工学部(に所属する研究者たちで構成されていた。電気・コンピューター工学科の研究者は、チー・ジア(Qi Jia)、ウィリアム・エクテンカンプ(William Echtenkamp)、ブランドン・ジンク(Brandon Zink)の各氏。機械工学科の研究者は、ディンビン・フアン(Dingbin Huang)、シャオジャ・ワン(Xiaojia Wang)准教授。特性評価施設(Characterization Facility)の研究者は、ハヴィエル・ガルシア=バリオカナル(Javier Garcia-Barriocanal)、ジョフリー・ロハス(Geoffrey Rojas)、グイチャン・ユ(Guichuan Yu)の各氏。NISTの研究者ジェニー・シャウプ(Jenae Shoup)も、今回の研究に貢献した。

研究論文:Sputtered L10-FePd and its synthetic antiferromagnet on Si/SiO2 wafers for scalable spintronics

この記事は、SpaceDaily.comが執筆し、Industry Dive Content Marketplaceを通じてライセンスされたものです。ライセンスに関するお問い合わせはlegal@industrydive.comまでお願いいたします。

![]()